-

- RF Series

- Connector&plug-in unit

- Plug-in unit

- SD card holder

- SIM card holder

- Thimble /wire protector

- Crimping terminal

- Waterproof joint

- 短路帽/跳线帽

- 压线端子胶壳

- 屏蔽夹

- Waterproof and dustproof terminal

- Industrial&automotive&military

发布时间:2025-05-30作者来源:金航标浏览:1392

USB接口是我们HW设计中使用的比较多的一个电路模块,特别是在医疗电子,商业电子电路中使用的比较多,以下我们来分享下USB接口和相对应的电路设计。

USB接口理论认识:

USB(Universal Serial Bus)通用串行总线,USB接口现在大致可以分为USB2.0,USB3.0,USB4(需要注意的是它的正式书写名字不包含空格也没有小数点,即不是USB 4,也不是USB4.0。USB4规范使用双链路通道,传输带宽达到40Gbps,接口类型为双向USB-C)。其中我们现在大部分使用的还是USB2.0和USB 3.2 Gen 1(前称为USB 3.0,后来重新命名为USB 3.1 Gen 1,最终被称为USB 3.2 Gen 1。)USB 3.2 Gen 2前称为USB 3.1,后改名为USB 3.2 Gen 2。与Gen 1相比,Gen 2在速度上有所提升。最大传输速度:10 Gbps,是Gen 1速度的两倍,称为SuperSpeed+。兼容性:向下兼容USB 3.2 Gen 1和USB 2.0。接下来我们来详细介绍下USB2.0和USB3.0在硬件电路设计上的区分和使用。

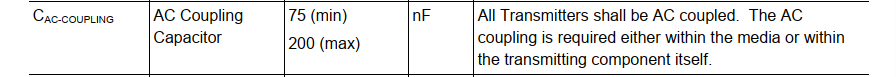

|

版本 |

最大传输速率 |

最大输出电流 |

前称 |

针脚数量 |

|

USB2.0 |

480Mbps |

500ma |

4个(VBUS/GND/D+/D-) |

|

|

USB3.1 GEN1 |

5Gbps |

900ma(标准端口) |

USB 3.1 Gen 1 和 USB 3.0 |

9个 |

|

USB3.1 GEN2 |

10 Gbps |

900ma(标准端口) |

USB 3.1 Gen 2 |

9个 |

USB硬件电路设计:

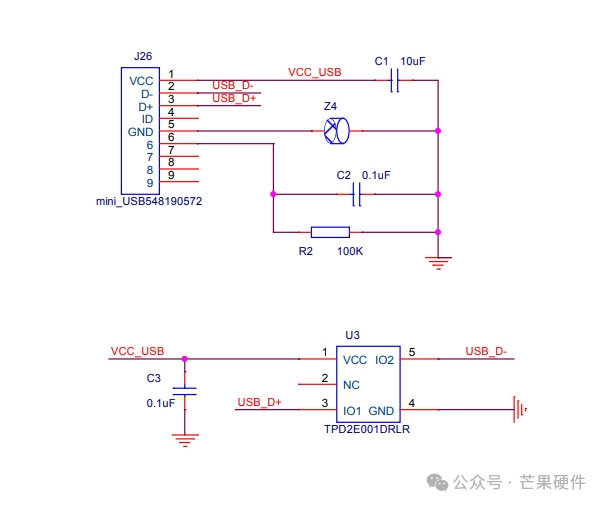

i)USB2.0包含了一组差分信号、一组电源信号(5V电源+GND),4线。

一般而言,上图的电路设计已经可以实现USB数据的正常传输了。但一般如果考虑EMC方面的话,最好在靠近USB插座端的地方加上共模电感,防止板子内部的高频干扰通过USB线辐射到外面,对其他的模块和设备造成电磁干扰。D+、D-以差分方式布线,并通过连续的参考平面层,保证阻抗的一致性,信号线的差分阻抗Z=90Ω±15%。

另外,稍微提一句USB_OTG(On-The-Go)允许设备在主机和外设角色间切换,通过ID引脚的状态确定设备角色。ID pin——当设备检测到USB_ID信号为低时,该设备应作为Host(主机,也称A设备)用。当设备检测到USB_ID信号为高时,该设备作为Slave(外设,也称B设备)用。

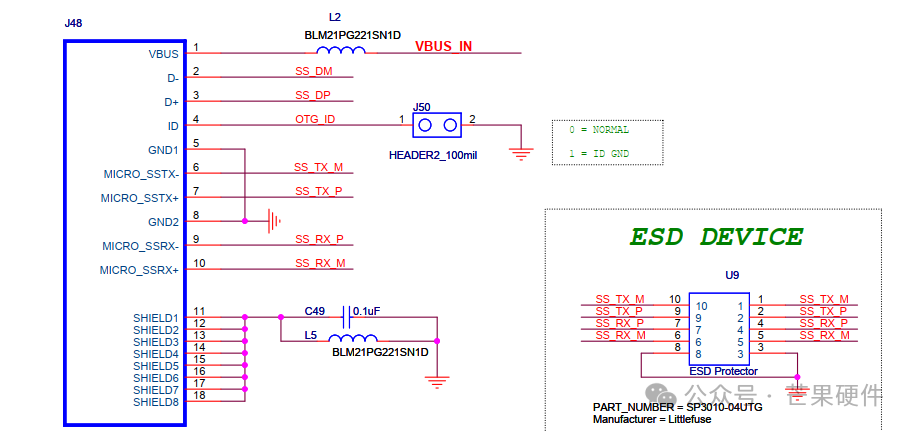

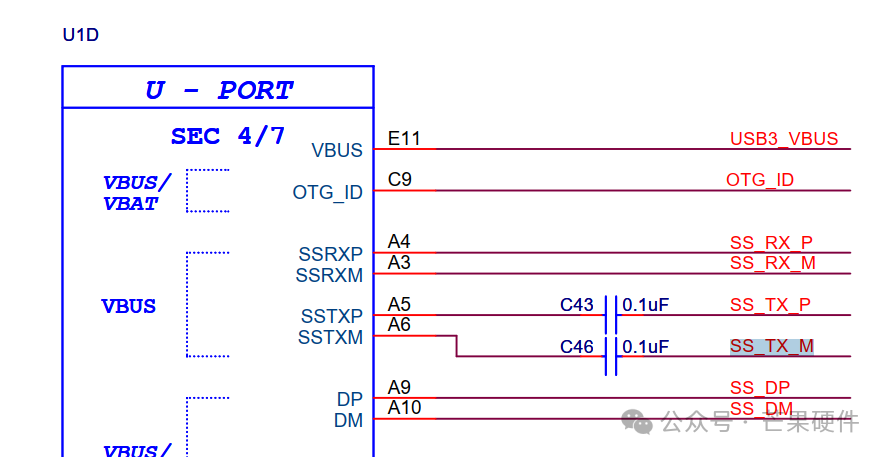

ii)USB3.0包含了一组2.0数据差分信号(D-、D+)、一组电源信号(5V电源、GND电源地)、二组3.0数据差分信号(RX-、RX+、TX-、TX+)、GND信号地,9线。

USB3.0由于采用的全双工通信模式(USB2.0 采用半双工通信模式),数据可以同时进行发送和接收,充分利用了传输带宽,数据传输速率(5Gbps/10 Gbps)。

DM/DP差分对信号线与USB2.0的连接方式一样,只要一对一直接连接就可以。信号线的差分阻抗Z=90Ω±10%。另外提醒下USB3.0在选型ESD防护二极管的时候要注意ESD寄生电容要小(0.5pf左右)。

RX-、RX+、TX-、TX+差分对属于高速serdes差分对,速度5Gbps/10 Gbps。需要在TX端放置100nF隔直电容(协议中规定是75nf-200nf),RX端无需放置。host端和device端的偏置直流电压值不一样,AC耦合电容起到隔直流作用,也可以更好的预制共模噪声。

免责声明:本文采摘自芒果硬件,本文仅代表作者个人观点,不代表金航标及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。

Copyright © Shenzhen Kinghelm Electronics Co., Ltd. all rights reservedYue ICP Bei No. 17113853